JANUARY 2007

#### **GENERAL DESCRIPTION**

The XRT86VL34 is a four-channel 1.544 Mbit/s or 2.048 Mbit/s DS1/E1/J1 framer and LIU integrated solution featuring R<sup>3</sup> technology (Relayless, Reconfigurable, Redundancy). The physical interface is optimized with internal impedance, and with the patented pad structure, the XRT86VL34 provides protection from power failures and hot swapping.

The XRT86VL34 contains an integrated DS1/E1/J1 framer and LIU which provide DS1/E1/J1 framing and error accumulation in accordance with ANSI/ITU\_T specifications. Each framer has its own framing synchronizer and transmit-receive slip buffers. The slip buffers can be independently enabled or disabled as required and can be configured to frame to the common DS1/E1/J1 signal formats.

Each Framer block contains its own Transmit and Receive T1/E1/J1 Framing function. There are 3 Transmit HDLC controllers per channel which encapsulate contents of the Transmit HDLC buffers into LAPD Message frames. There are 3 Receive HDLC controllers per channel which extract the payload content of Receive LAPD Message frames from the incoming T1/E1/J1 data stream and write the contents into the Receive HDLC buffers. Each framer also contains a Transmit and Overhead Data Input port, which permits Data Link Terminal Equipment direct access to the outbound T1/E1/J1 frames. Likewise, a Receive Overhead output data port permits Data Link Terminal Equipment direct access to the Data Link bits of the inbound T1/E1/J1 frames.

The XRT86VL34 fully meets all of the latest T1/E1/J1 specifications: ANSI T1/E1.107-1988, ANSI T1/E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/E1.408-1990, AT&T TR 62411 (12-90) TR54016, and ITU G-703, G.704, G706 and G.733, AT&T Pub. 43801, and ETS 300 011, 300 233, JT G.703, JT G.704, JT G706, I.431. Extensive test and diagnostic functions include Loop-backs, Boundary scan, Pseudo Random bit sequence (PRBS) test pattern generation, Performance Monitor, Bit Error Rate (BER) meter, forced error insertion, and LAPD unchannelized data payload processing according to ITU-T standard Q.921.

#### Applications and Features (next page)

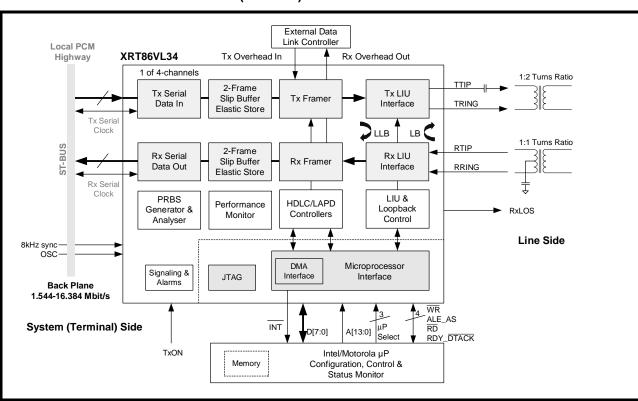

FIGURE 1. XRT86VL34 4-CHANNEL DS1 (T1/E1/J1) FRAMER/LIU COMBO

#### QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

#### **APPLICATIONS**

- High-Density T1/E1/J1 interfaces for Multiplexers, Switches, LAN Routers and Digital Modems

- SONET/SDH terminal or Add/Drop multiplexers (ADMs)

- T1/E1/J1 add/drop multiplexers (MUX)

- Channel Service Units (CSUs): T1/E1/J1 and Fractional T1/E1/J1

- Digital Access Cross-connect System (DACs)

- Digital Cross-connect Systems (DCS)

- Frame Relay Switches and Access Devices (FRADS)

- ISDN Primary Rate Interfaces (PRA)

- PBXs and PCM channel bank

- T3 channelized access concentrators and M13 MUX

- Wireless base stations

- ATM equipment with integrated DS1 interfaces

- Multichannel DS1 Test Equipment

- T1/E1/J1 Performance Monitoring

- Voice over packet gateways

- Routers

#### FEATURES

- Four independent, full duplex DS1 Tx and Rx Framer/LIUs

- Two 512-bit (two-frame) elastic store, PCM frame slip buffers (FIFO) on TX and Rx provide up to 8.192 MHz asynchronous back plane connections with jitter and wander attenuation

- Supports input PCM and signaling data at 1.544, 2.048, 4.096 and 8.192 Mbits. Also supports 4-channel multiplexed 12.352/16.384 (HMVIP/H.100) Mbit/s on the back plane bus

- Programmable output clocks for Fractional T1/E1/J1

- Supports Channel Associated Signaling (CAS)

- Supports Common Channel Signalling (CCS)

- Supports ISDN Primary Rate Interface (ISDN PRI) signaling

- Extracts and inserts robbed bit signaling (RBS)

- 3 Integrated HDLC controllers per channel for transmit and receive, each controller having two 96-byte buffers (buffer 0 / buffer 1)

- HDLC Controllers Support SS7

- Timeslot assignable HDLC

- V5.1 or V5.2 Interface

- Automatic Performance Report Generation (PMON Status) can be inserted into the transmit LAPD interface every 1 second or for a single transmission

- Alarm Indication Signal with Customer Installation signature (AIS-CI)

- Remote Alarm Indication with Customer Installation (RAI-CI)

- Gapped Clock interface mode for Transmit and Receive.

Experience Our Connectivity... REV. V1.2.0

## QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

XRT86VL34

- Intel/Motorola and Power PC interfaces for configuration, control and status monitoring

- Parallel search algorithm for fast frame synchronization

- Wide choice of T1 framing structures: SF/D4, ESF, SLC®96, T1DM and N-Frame (non-signaling)

- Direct access to D and E channels for fast transmission of data link information

- PRBS, QRSS, and Network Loop Code generation and detection

- Programmable Interrupt output pin

- Supports programmed I/O and DMA modes of Read-Write access

- Each framer block encodes and decodes the T1/E1/J1 Frame serial data

- Detects and forces Red (SAI), Yellow (RAI) and Blue (AIS) Alarms

- Detects OOF, LOF, LOS errors and COFA conditions

- Loopbacks: Local (LLB) and Line remote (LB)

- Facilitates Inverse Multiplexing for ATM

- Performance monitor with one second polling

- Boundary scan (IEEE 1149.1) JTAG test port

- Accepts external 8kHz Sync reference

- 1.8V Inner Core

- 3.3V CMOS operation with 5V tolerant inputs

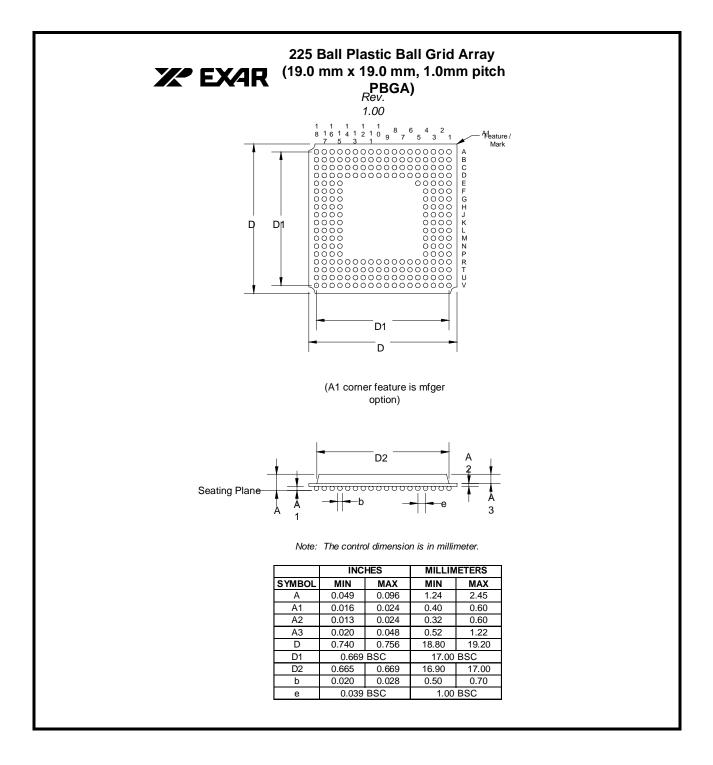

- 225-pin PBGA package with -40°C to +85°C operation

## ORDERING INFORMATION

| PART NUMBER | PACKAGE                     | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------------|-----------------------------|

| XRT86VL34IB | 225 Plastic Ball Grid Array | -40°C to +85°C              |

# LIST OF PARAGRAPHS

# LIST OF TABLES

| Table 1:: List by Pin Number                                                        | 4  |

|-------------------------------------------------------------------------------------|----|

| Table 2                                                                             | 6  |

| Table 3:: Pin Description Structure                                                 | 6  |

| Table 4:: XRT86VL34 Power Consumption                                               | 41 |

| Table 5:: E1 Receiver Electrical Characteristics                                    |    |

| Table 6:: T1 Receiver Electrical Characteristics                                    | 50 |

| Table 7:: E1 Transmitter Electrical Characteristics                                 | 50 |

| Table 8:: E1 Transmit Return Loss Requirement                                       | 51 |

| Table 9:: T1 Transmitter Electrical Characteristics                                 | 51 |

| Table 10:: Transmit Pulse Mask Specification                                        |    |

| Table 11:: DSX1 Interface Isolated pulse mask and corner points                     | 53 |

| Table 12:: AC Electrical Characteristics                                            | 54 |

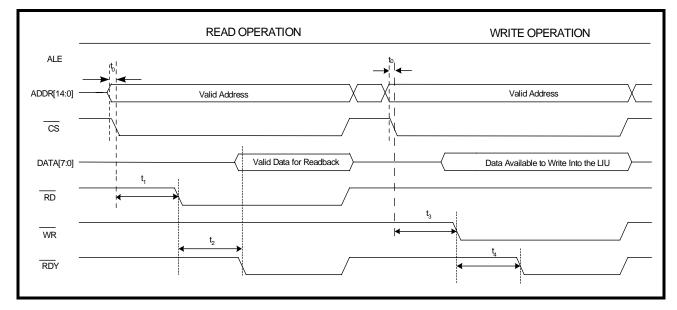

| Table 13:: Intel Microprocessor Interface Timing Specifications                     |    |

| Table 14:: Intel Microprocessor Interface Timing Specifications                     | 56 |

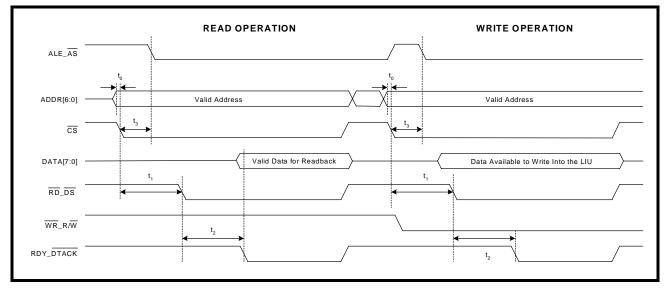

| Table 15:: Motorola Asychronous Mode Microprocessor Interface Timing Specifications | 57 |

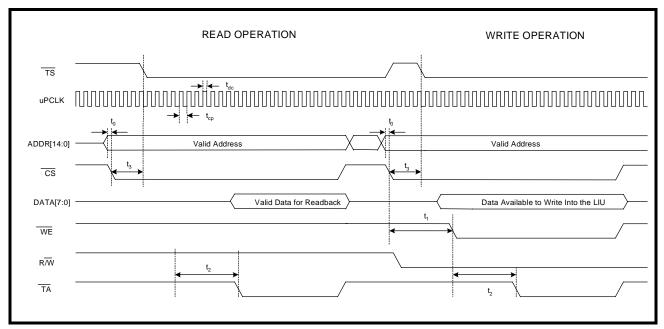

| Table 16:: Power PC 403 Microprocessor Interface Timing Specifications              | 58 |

## QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

# **LIST OF FIGURES**

| Figure 1.: XRT86VL34 4-channel DS1 (T1/E1/J1) Framer/LIU Combo                                                    | 1    |

|-------------------------------------------------------------------------------------------------------------------|------|

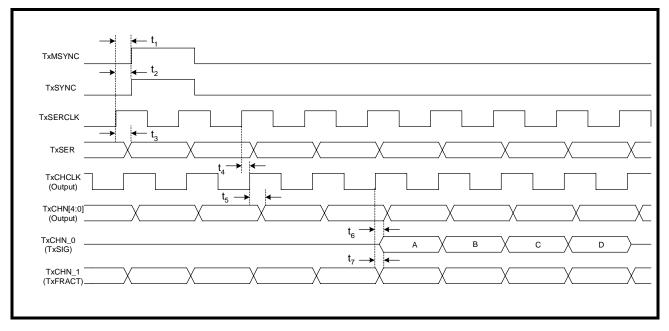

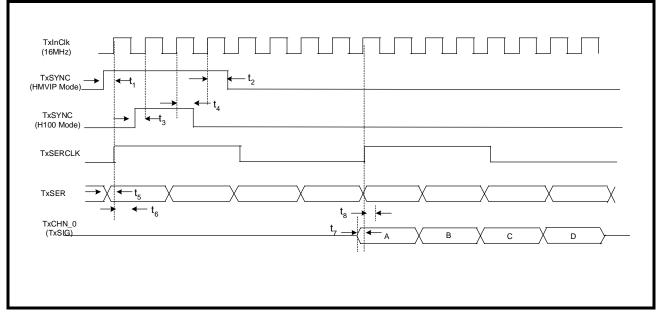

| Figure 2.: Framer System Transmit Timing Diagram (Base Rate/Non-Mux)                                              | 2    |

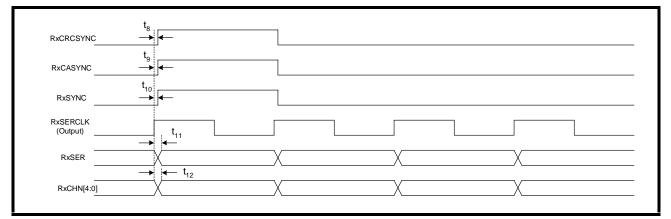

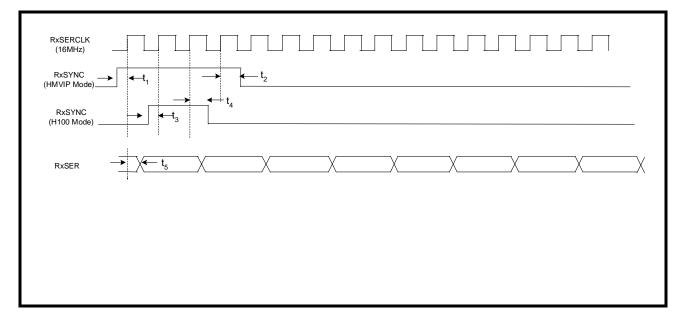

| Figure 3.: Framer System Receive Timing Diagram (RxSERCLK as an Output)4                                          | 3    |

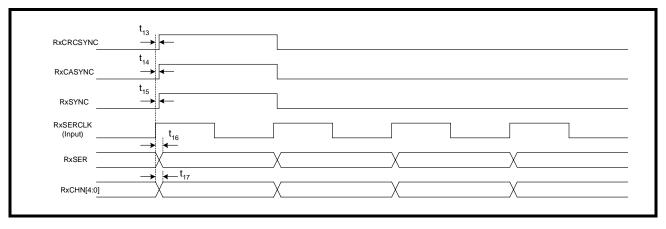

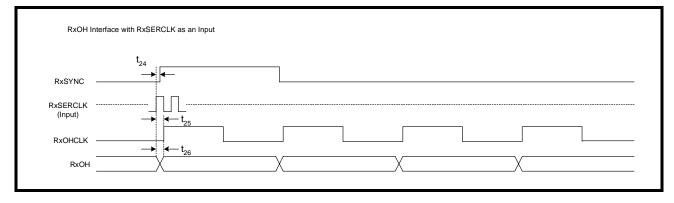

| Figure 4.: Framer System Receive Timing Diagram (RxSERCLK as an Input)4                                           | 4    |

| Figure 5.: Framer System Transmit Timing Diagram (HMVIP and H100 Mode)4                                           | 5    |

| Figure 6.: Framer System Receive Timing Diagram (HMVIP/H100 Mode)4                                                | 6    |

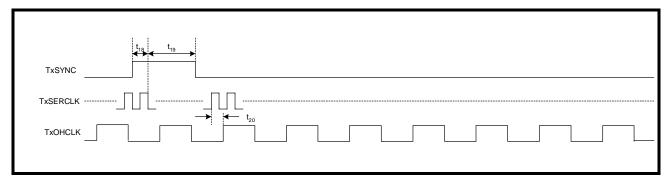

| Figure 7.: Framer System Transmit Overhead Timing Diagram                                                         | 7    |

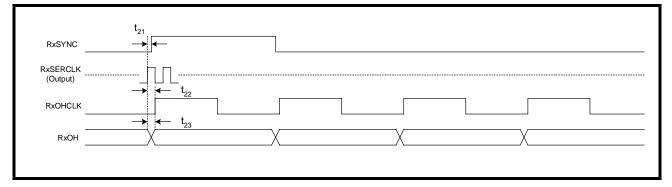

| Figure 8.: Framer System Receive Overhead Timing Diagram (RxSERCLK as an Output)                                  | 8    |

| Figure 9.: Framer System Receive Overhead Timing Diagram (RxSERCLK as an Input)4                                  | 8    |

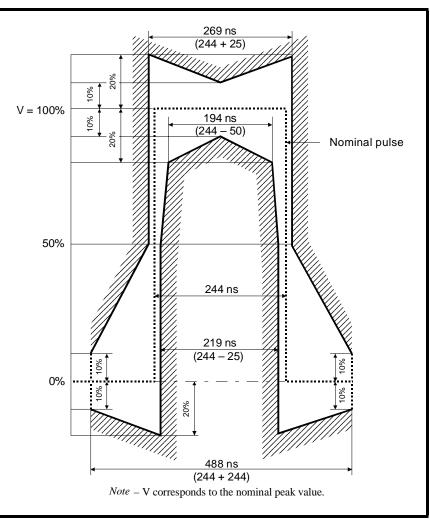

| Figure 10.: ITU G.703 Pulse Template                                                                              | 2    |

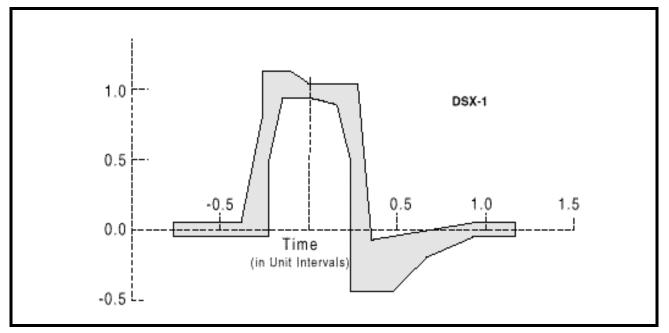

| Figure 11.: DSX-1 Pulse Template (normalized amplitude)5                                                          | 3    |

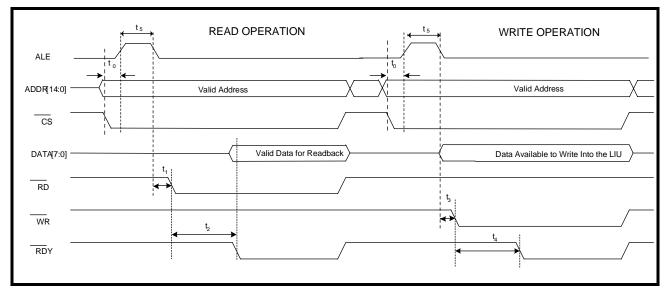

| Figure 12.: Intel µP Interface Timing During Programmed I/O Read and Write Operations When ALE Is Not Tied 'HIGH' | ' 55 |

| Figure 13.: Intel µP Interface Timing During Programmed I/O Read and Write Operations When ALE Is Tied 'HIGH' 5   | 6    |

| Figure 14.: Motorola Asychronous Mode Interface Signals During Programmed I/O Read and Write Operations 5         | 7    |

| Figure 15.: Power PC 403 Interface Signals During Programmed I/O Read and Write Operations                        | 8    |

Experience *Our* Connectivity... *REV. V1.2.0*

# XRT86VL34 QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

TABLE 1: LIST BY PIN

|     | NUMBER     | E |

|-----|------------|---|

| ΡιΝ | PIN NAME   | E |

| A1  | GNDPLL     | E |

| A2  | AVDD18     | E |

| A3  | E1MCLKnOUT |   |

| A4  | MCLKIN     |   |

| A5  | VSS        | ( |

| A6  | TRST       |   |

| A7  | RXSERCLK0  |   |

| A8  | RXCHCLK0   | ( |

| A9  | RXOHCLK0   | ( |

| A10 | TXMSYNC0   | ( |

| A11 | TXOHCLK0   | ( |

| A12 | TXSERCLK0  | C |

| A13 | TXCHCLK0   | C |

| A14 | TXCHN0_3   | C |

| A15 | RXSER1     | C |

| A16 | RXCHCLK1   | C |

| A17 | RXCHN1_2   | C |

| A18 | RXSYNC1    | C |

| B1  | VDDPLL18   | C |

| B2  | JTAG_Ring  | C |

| B3  | AGND       |   |

| B4  | T1MCLKnOUT |   |

| B5  | aTESTMODE  |   |

| B6  | TDI        |   |

| B7  | RXLOS0     |   |

| B8  | DVDD18     |   |

| B9  | RXCHN0_2   |   |

| B10 | RXCHN0_4   |   |

| B11 | TESTMODE   |   |

| B12 | TXCHN0_0   |   |

| B13 | TXCHN0_2   |   |

| B14 | VSS        |   |

|     |            |   |

| PIN         PIN NAME           B15         RXCHN1_1           B16         RXOH1           B17         RXCASYNC1           B18         TXSYNC1           C1         GNDPLL           C2         VDDPLL18           C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHO           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0  |     |            |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|--|--|--|

| B16         RXOH1           B17         RXCASYNC1           B18         TXSYNC1           C1         GNDPLL           C2         VDDPLL18           C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                 | PIN | PIN NAME   |  |  |  |

| B17         RXCASYNC1           B18         TXSYNC1           C1         GNDPLL           C2         VDDPLL18           C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCH0           C11         RXON_4           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0 | B15 | RXCHN1_1   |  |  |  |

| B18         TXSYNC1           C1         GNDPLL           C2         VDDPLL18           C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                    | B16 | RXOH1      |  |  |  |

| C1         GNDPLL           C2         VDDPLL18           C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCH0           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                                                     | B17 | RXCASYNC1  |  |  |  |

| C2         VDDPLL18           C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                                                                                                                                       | B18 | TXSYNC1    |  |  |  |

| C3         JTAG_Tip           C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCH0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                                                                                                                                                                      | C1  | GNDPLL     |  |  |  |

| C4         DVDD18           C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                                                                                                                                                                                                   | C2  | VDDPLL18   |  |  |  |

| C5         DGND           C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCH0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D10         RXCASYNC0                                                                                                                                                                                                                                                                             | C3  | JTAG_Tip   |  |  |  |

| C6         TMS           C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D10         RXCASYNC0                                                                                                                                                                                                                                                                                                      | C4  | DVDD18     |  |  |  |

| C7         TCLK           C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D10         RXCASYNC0                                                                                                                                                                                                                                                                                                                               | C5  | DGND       |  |  |  |

| C8         RXCRCSYNC0           C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                                                                                                                                                                                                                                                                                                            | C6  | TMS        |  |  |  |

| C9         RXCHN0_1           C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D9         TXSYNC0           D10         RXCASYNC0                                                                                                                                                                                                                                                                                                                                                            | C7  | TCLK       |  |  |  |

| C10         RXCHN0_3           C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D10         RXCASYNC0           D11         TXSER0                                                                                                                                                                                                                                                                                                                                                                                          | C8  | RXCRCSYNC0 |  |  |  |

| C11         RXOH0           C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D10         RXCASYNC0           D11         TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                         | C9  | RXCHN0_1   |  |  |  |

| C12         TXOH0           C13         RXCRCSYNC1           C14         TXCHN0_4           C15         TXCHCLK1           C16         VSS           C17         TXMSYNC1           C18         RXLOS1           D1         GNDPLL           D2         VDDPLL18           D3         VDDPLL18           D4         GNDPLL           D5         TDO           D6         RXSER0           D7         RXCHN0_0           D8         RXSYNC0           D10         RXCASYNC0           D11         TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                     | C10 | RXCHN0_3   |  |  |  |

| C13RXCRCSYNC1C14TXCHN0_4C15TXCHCLK1C16VSSC17TXMSYNC1C18RXLOS1D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C11 | RXOH0      |  |  |  |

| C14TXCHN0_4C15TXCHCLK1C16VSSC17TXMSYNC1C18RXLOS1D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C12 | TXOH0      |  |  |  |

| C15TXCHCLK1C16VSSC17TXMSYNC1C18RXLOS1D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | C13 | RXCRCSYNC1 |  |  |  |

| C16VSSC17TXMSYNC1C18RXLOS1D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C14 | TXCHN0_4   |  |  |  |

| C17TXMSYNC1C18RXLOS1D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C15 | TXCHCLK1   |  |  |  |

| C18RXLOS1D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C16 | VSS        |  |  |  |

| D1GNDPLLD2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C17 | TXMSYNC1   |  |  |  |

| D2VDDPLL18D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C18 | RXLOS1     |  |  |  |

| D3VDDPLL18D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | D1  | GNDPLL     |  |  |  |

| D4GNDPLLD5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D2  | VDDPLL18   |  |  |  |

| D5TDOD6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D3  | VDDPLL18   |  |  |  |

| D6RXSER0D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | D4  | GNDPLL     |  |  |  |

| D7RXCHN0_0D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D5  | TDO        |  |  |  |

| D8RXSYNC0D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D6  | RXSER0     |  |  |  |

| D9TXSYNC0D10RXCASYNC0D11TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | D7  |            |  |  |  |

| D10 RXCASYNC0<br>D11 TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D8  | RXSYNC0    |  |  |  |

| D11 TXSER0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D9  | TXSYNC0    |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D10 | RXCASYNC0  |  |  |  |

| D12 TXCHN0_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D11 | TXSER0     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D12 | TXCHN0_1   |  |  |  |

| PIN PIN NAME |           |  |  |

|--------------|-----------|--|--|

| D13          | RXSERCLK1 |  |  |

| D14          | RXCHN1_0  |  |  |

| D15          | RXSERCLK2 |  |  |

| D16          | VDD       |  |  |

| D17          | RXOHCLK1  |  |  |

| D18          | RXCHN1_3  |  |  |

| E1           | RTIP0     |  |  |

| E2           | RGND0     |  |  |

| E3           | RVDD0     |  |  |

| E4           | TTIP0     |  |  |

| E5           | ANALOG    |  |  |

| E15          | TXOHCLK1  |  |  |

| E16          | TXSER1    |  |  |

| E17          | RXCHN1_4  |  |  |

| E18          | TXSERCLK1 |  |  |

| F1           | RRING0    |  |  |

| F2           | TGND0     |  |  |

| F3           | TVDD0     |  |  |

| F4           | TRING0    |  |  |

| F15          | TXOH1     |  |  |

| F16          | TXCHN1_0  |  |  |

| F17          | TXCHN1_1  |  |  |

| F18          | RXSYNC2   |  |  |

| G1           | RTIP1     |  |  |

| G2           | RGND1     |  |  |

| G3           | RVDD1     |  |  |

| G4           | TTIP1     |  |  |

| G15          | RXCHN2_1  |  |  |

| G16          | RXLOS2    |  |  |

| G17          | TXCHN1_2  |  |  |

| G18          | TXCHN1_3  |  |  |

| H1           | RRING1    |  |  |

| H2           | TGND1     |  |  |

| H3           | TVDD1     |  |  |

| DWARE DESCRIPTION |            |  |  |  |

|-------------------|------------|--|--|--|

| PIN PIN NAME      |            |  |  |  |

| H4                | TRING1     |  |  |  |

| H15               | RXCASYNC2  |  |  |  |

| H16               | RXCHN2_0   |  |  |  |

| H17               | RXCHCLK2   |  |  |  |

| H18               | TXCHN1_4   |  |  |  |

| J1                | RTIP2      |  |  |  |

| J2                | RGND2      |  |  |  |

| J3                | RVDD2      |  |  |  |

| J4                | TTIP2      |  |  |  |

| J15               | TXSERCLK2  |  |  |  |

| J16               | DVDD18     |  |  |  |

| J17               | RXCRCSYNC2 |  |  |  |

| J18               | RXSER2     |  |  |  |

| K1                | RRING2     |  |  |  |

| K2                | TGND2      |  |  |  |

| K3                | TVDD2      |  |  |  |

| K4                | TRING2     |  |  |  |

| K15               | RXOH2      |  |  |  |

| K16               | RXCHN2_4   |  |  |  |

| K17               | RXOHCLK2   |  |  |  |

| K18               | RXCHN2_2   |  |  |  |

| L1                | RTIP3      |  |  |  |

| L2                | RGND3      |  |  |  |

| L3                | RVDD3      |  |  |  |

| L4                | TTIP3      |  |  |  |

| L15               | TXSYNC2    |  |  |  |

| L16               | RXCHN2_3   |  |  |  |

| L17               | TXMSYNC2   |  |  |  |

| L18               | TXSER2     |  |  |  |

| M1                | RRING3     |  |  |  |

| M2                | TGND3      |  |  |  |

| M3                | TVDD3      |  |  |  |

| M4                | TRING3     |  |  |  |

| M15               | VSS        |  |  |  |

|                   |            |  |  |  |

# QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

| ΡιΝ | PIN NAME  |  |

|-----|-----------|--|

| M16 | VSS       |  |

| M17 | TXCHN2_1  |  |

| M18 | TXCHN2_0  |  |

| N1  | TxON      |  |

| N2  | LOP       |  |

| N3  | RXTSEL    |  |

| N4  | 8KEXTOSC  |  |

| N15 | TXCHN2_4  |  |

| N16 | TXCHN2_3  |  |

| N17 | TXCHCLK2  |  |

| N18 | TXOHCLK2  |  |

| P1  | RESET     |  |

| P2  | E1OSCCLK  |  |

| P3  | VDD       |  |

| P4  | T1OSCCLK  |  |

| P15 | TXOH2     |  |

| P16 | RXSYNC3   |  |

| P17 | RXCHNCLK3 |  |

| P18 | RXOH3     |  |

| R1  | REQ0      |  |

| R2  | 8KSYNC    |  |

| R3  | REQ1      |  |

| R4  | VSS       |  |

| R5  | ADDR2     |  |

| R6  | ADDR6     |  |

| R7  | ADDR10    |  |

| R8  | INT       |  |

| R9  | ADDR11    |  |

| R10 | ADDR12    |  |

| R11 | DATA7     |  |

| R12 | TXMSYNC3  |  |

| R13 | DVDD18    |  |

| R14 | ТХОН3     |  |

| R15 | VDD       |  |

| ΡιΝ | PIN NAME   |

|-----|------------|

| R16 | RXOHCLK3   |

| R17 | RXCRCSYNC3 |

| R18 | RXCHN3_0   |

| T1  | fADDR      |

| T2  | ACK0       |

| Т3  | RDY        |

| T4  | DATA0      |

| T5  | VSS        |

| Т6  | ADDR3      |

| T7  | ADDR7      |

| Т8  | PTYPE2     |

| Т9  | VDD        |

| T10 | DATA4      |

| T11 | TXCHN3_4   |

| T12 | TXCHN3_2   |

| T13 | TXCHN3_0   |

| T14 | RXCHN3_3   |

| T15 | RXCHN3_2   |

| T16 | TXCHN2_2   |

| T17 | RXSERCLK3  |

| T18 | RXCASYNC3  |

| U1  | iADDR      |

| U2  | ACK1       |

| U3  | DATA1      |

| U4  | DBEN       |

| U5  | ADDR0      |

| U6  | ADDR4      |

| U7  | DVDD18     |

| U8  | ALE        |

| U9  | ADDR9      |

| U10 | BLAST      |

| U11 | DATA6      |

| U12 | TXCHN3_3   |

| U13 | TXCHN3_1   |

| ΡιΝ | PIN NAME  |  |  |

|-----|-----------|--|--|

| U14 | RXCHN3_4  |  |  |

| U15 | TXSYNC3   |  |  |

| U16 | VSS       |  |  |

| U17 | RXSER3    |  |  |

| U18 | RLOS3     |  |  |

| V1  | PCLK      |  |  |

| V2  | PTYPE0    |  |  |

| V3  | RD        |  |  |

| V4  | PTYPE1    |  |  |

| V5  | ADDR1     |  |  |

| V6  | ADDR5     |  |  |

| V7  | ADDR8     |  |  |

| V8  | DATA2     |  |  |

| V9  | DATA3     |  |  |

| V10 | DATA5     |  |  |

| V11 | ADDR13    |  |  |

| V12 | WR        |  |  |

| V13 | CS        |  |  |

| V14 | TXSER3    |  |  |

| V15 | TXSERCLK3 |  |  |

| V16 | TXOHCLK3  |  |  |

| V17 | TXCHCLK3  |  |  |

| V18 | RXCHN3_1  |  |  |

#### **1.0 PIN DESCRIPTIONS**

There are five types of pins defined throughout this pin description and the corresponding symbol is presented in table below. The per-channel pin is indicated by the channel number or the letter 'n' which is appended at the end of the signal name, for example, TxSERn, where "n" indicates channels 0 to 3. All output pins are "tri-stated" upon hardware RESET

| TA | BL | E | 2 | : |

|----|----|---|---|---|

|    |    |   |   |   |

| Symbol | Pin Type      |

|--------|---------------|

| I      | Input         |

| 0      | Output        |

| I/O    | Bidirectional |

| GND    | Ground        |

| PWR    | Power         |

The structure of the pin description is divided into twelve groups, as presented in the table below

| SECTION                        | PAGE NUMBER |  |  |

|--------------------------------|-------------|--|--|

| Transmit System Side Interface | page 7      |  |  |

| Transmit Overhead Interface    | page 15     |  |  |

| Receive Overhead Interface     | page 17     |  |  |

| Receive System Side Interface  | page 18     |  |  |

| Receive Line Interface         | page 26     |  |  |

| Transmit Line Interface        | page 28     |  |  |

| Timing Interface               | page 28     |  |  |

| JTAG Interface                 | page 30     |  |  |

| Microprocessor Interface       | page 31     |  |  |

| Power Pins (3.3V)              | page 39     |  |  |

| Power Pins (1.8V)              | page 39     |  |  |

| Ground Pins                    | page 40     |  |  |

#### TABLE 3: PIN DESCRIPTION STRUCTURE

#### QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

| SIGNAL NAME       | BALL# | Түре | OUTPUT<br>DRIVE(MA) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-------|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxSER0/<br>TxPOS0 | D11   | I    | -                   | Transmit Serial Data Input (TxSERn)/Transmit Positive Digital Input (TxPOSn):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TxSER1/<br>TxPOS1 | E16   |      |                     | The exact function of these pins depends on the mode of operation selected, as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TxSER2/           | L18   |      |                     | DS1/E1 Mode - TxSERn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TxPOS2            |       |      |                     | These pins function as the transmit serial data input on the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TxSER3/<br>TxPOS3 | V14   |      |                     | side interface, which are latched on the rising edge of the TxSER-<br>CLKn pin. Any payload data applied to this pin will be inserted into an<br>outbound DS1/E1 frame and output to the line. In DS1 mode, the<br>framing alignment bits, facility data link bits, CRC-6 bits, and signaling<br>information can also be inserted from this input pin if configured<br>appropriately. In E1 mode, all data intended to be transported via<br>Time Slots 1 through 15 and Time slots 17 through 31 must be<br>applied to this input pin. Data intended for Time Slots 0 and 16 can<br>also be applied to this input pin If configured accordingly. |

|                   |       |      |                     | DS1 or E1 High-Speed Multiplexed Mode* - TxSERn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   |       |      |                     | In this mode, these pins are used as the high-speed multiplexed data<br>input pin on the system side. High-speed multiplexed data of chan-<br>nels 0-3 must be applied to TxSER0 in a byte or bit-interleaved way.<br>The framer latches in the multiplexed data on TxSER0 using TxM-<br>SYNC/TxINCLK and demultiplexes this data into 4 serial streams.<br>The LIU block will then output the data to the line interface using<br>TxSERCLKn.                                                                                                                                                                                                     |

|                   |       |      |                     | DS1 or E1 Framer Bypass Mode - TxPOSn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   |       |      |                     | In this mode, TxSERn is used for the positive digital input pin (TxPOSn) to the LIU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   |       |      |                     | Νοτε:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   |       |      |                     | <ol> <li>*High-speed multiplexed modes include (For T1/E1)<br/>16.384MHz HMVIP, H.100, Bit-multiplexed modes, and (For<br/>T1 only) 12.352MHz Bit-multiplexed mode.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   |       |      |                     | <ol> <li>In DS1 high-speed modes, the DS-0 data is mapped into an<br/>E1 frame by ignoring every fourth time slot (don't care).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   |       |      |                     | <ol> <li>These 8 pins are internally pulled "High" for each channel.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

**XRT86VL34**

| SIGNAL NAME                            | BALL# | Түре | OUTPUT<br>DRIVE(MA) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------|-------|------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxSERCLK0/                             | A12   | I/O  | 12                  | Transmit Serial Clock (TxSERCLKn)/Transmit Line Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TxLINECLK0<br>TxSERCLK1/<br>TxLINECLK1 | E18   |      |                     | (TxSERCLKn):<br>The exact function of these pins depends on the mode of operation<br>selected, as described below.                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxSERCLK2/                             | J15   |      |                     | In Base-Rate Mode (1.544MHz/2.048MHz) - TxSERCLKn:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TxLINECLK2                             |       |      |                     | This clock signal is used by the transmit serial interface to latch the contents on the TxSERn pins into the T1/E1 framer on the rising edge                                                                                                                                                                                                                                                                                                                                                                                      |

| TxSERCLK3/<br>TxLINECLK3               | V15   |      |                     | of TxSERCLKn. These pins can be configured as input or output as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                        |       |      |                     | When TxSERCLKn is configured as Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                        |       |      |                     | These pins will be inputs if the TxSERCLK is chosen as the timing source for the transmit framer. Users must provide a 1.544MHz clock rate to this input pin for T1 mode of operation, and 2.048MHz clock rate in E1 mode.                                                                                                                                                                                                                                                                                                        |

|                                        |       |      |                     | When TxSERCLKn is configured as Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        |       |      |                     | These pins will be outputs if either the recovered line clock or the MCLK PLL is chosen as the timing source for the T1/E1 transmit framer. The transmit framer will output a 1.544MHz clock rate in T1 mode of operation, and a 2.048MHz clock rate in E1 mode.                                                                                                                                                                                                                                                                  |

|                                        |       |      |                     | DS1/E1 High-Speed Backplane Modes* - TxSERCLKn as INPUT<br>ONLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        |       |      |                     | In this mode, TxSERCLK is an optional clock signal input which is<br>used as the timing source for the transmit line interface, and is only<br>required if TxSERCLK is chosen as the timing source for the transmit<br>framer. If TxSERCLK is chosen as the timing source, system equip-<br>ment should provide 1.544MHz (For T1 mode) or 2.048MHz (For E1<br>mode) to the TxSERCLKn pins on each channel. TxSERCLK is not<br>required if either the recovered clock or MCLK PLL is chosen as the<br>timing source of the device. |

|                                        |       |      |                     | High speed or multiplexed data is latched into the device using the                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                        |       |      |                     | TxMSYNC/TxINCLK high-speed clock signal.<br>DS1 or E1 Framer Bypass Mode - TxLINECLKn                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                        |       |      |                     | In this mode, TxSERCLKn is used as the transmit line clock (TxLI-<br>NECLK) to the LIU.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                        |       |      |                     | Note: *High-speed backplane modes include (For T1/E1)<br>2.048MVIP, 4.096MHz, 8.192MHz, 16.384MHz HMVIP,<br>H.100, Bit-multiplexed modes, and (For T1 only) 12.352MHz<br>Bit-multiplexed mode.                                                                                                                                                                                                                                                                                                                                    |

|                                        |       |      |                     | <b>Note:</b> In DS1 high-speed modes, the DS-0 data is mapped into an E1 frame by ignoring every fourth time slot (don't care).                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                        |       |      |                     | <b>Note:</b> These 8 pins are internally pulled "High" for each channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### QUAD T1/E1/J1 FRAMER/LIU COMBO - HARDWARE DESCRIPTION

| SIGNAL NAME                  | BALL# | Түре | OUTPUT<br>DRIVE(MA) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|-------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxSYNC0/<br>TxNEG0           | D9    | I/O  | 12                  | Transmit Single Frame Sync Pulse (TxSYNCn) / Transmit Nega-<br>tive Digital Input (TxNEGn):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TxSYNC1/<br>TxNEG1           | B18   |      |                     | The exact function of these pins depends on the mode of operation selected, as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |